Couverture

Open Silicium

N°

Numéro

17

Numéro

17

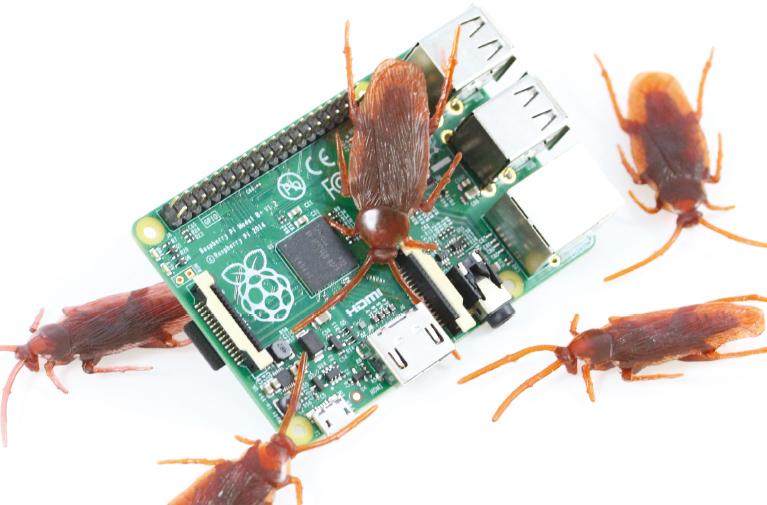

Chasse aux bugs noyau sur Raspberry Pi

Temporalité

Janvier/Février/Mars 2016

Dans ce numéro

Image v3

Article mis en avant

Résumé

La sonde JTAG est un équipement souvent coûteux réservé à des professionnels. C'est pourtant un outil indispensable pour la mise au point de programmes « bas niveau »...