Dans cet article, on se propose de découvrir une autre méthode de validation d’un composant écrit en Verilog. L’idée est de décrire les propriétés du composant et de laisser l’ordinateur chercher les stimuli qui feront échouer des propriétés. Ça n’est plus le développeur qui écrit les tests, mais la machine. Cette méthode a récemment été rendue possible avec des logiciels libres grâce à la suite d’outils Yosys (synthèse Verilog), Yosys-SMTBMC (solveur) ainsi que SymbiYosys qui les chapeaute.

Quand on développe un composant numérique avec un langage HDL comme le Verilog, il est obligatoire de vérifier son comportement en simulation. Cette simulation consiste à décrire l’évolution des valeurs d’entrée du bloc au cours du temps et de vérifier que les valeurs de sortie soient celles attendues.

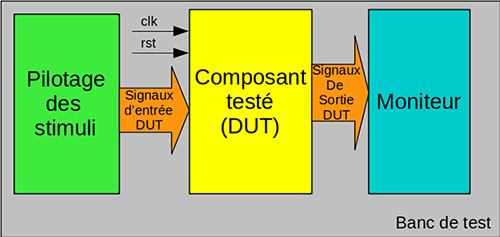

Il est quasiment impossible de faire quelque chose qui soit un minimum complexe sur FPGA sans passer par cette étape. La manière classique de faire consiste à écrire un bloc « banc de test » comme en figure 1 qui inclura (instanciation) le bloc HDL à tester.

- Accédez à tous les contenus de Connect en illimité

- Découvrez des listes de lecture et des contenus Premium

- Consultez les nouveaux articles en avant-première

Ajouter à une liste de lecture

Ajouter à une liste de lecture