Pour évaluer un nouveau FPGA, on commence généralement avec la conception d’un compteur pour faire clignoter une LED. Ce HelloWorld simpliste nous amène à utiliser toute la chaîne de développement, de la conception du circuit en langage HDL jusqu’à la configuration du FPGA sur le kit. En passant bien sûr par la synthèse, le placement routage et le bitstream. On se penche rarement sur les performances du compteur utilisé pour le clignotement ni comment l’optimiser de manière à augmenter la fréquence de cadencement au maximum qu’il est possible d’obtenir avec le modèle étudié. C’est pourtant ce qu’on se propose de faire dans cet article à partir du kit iCEstick de chez Lattice.

Alors voilà, on vient de recevoir un nouveau kit de développement FPGA. Quelle est la première chose que nous pouvons faire avec ça ?

Faire clignoter une LED, pardi !

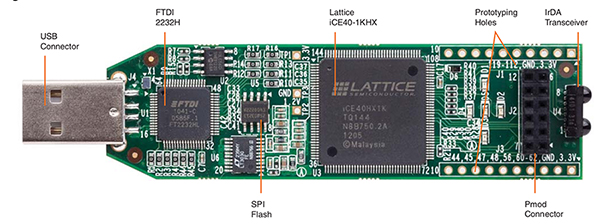

Prenons l’exemple du célèbre kit « clef USB » [1] de Lattice. Célèbre, car il est basé sur le premier FPGA à avoir été complètement « rétro-ingénieré » pour être utilisable 100 % avec des outils open source : le iCE40 (voir le feu Open Silicium [2]).

- Accédez à tous les contenus de Connect en illimité

- Découvrez des listes de lecture et des contenus Premium

- Consultez les nouveaux articles en avant-première

Ajouter à une liste de lecture

Ajouter à une liste de lecture