Derrière les annonces sur l’initiative Google/Skywater, à l'heure où NVIDIA rachète ARM et donc booste mécaniquement RISC-V, c'est toute une industrie qui va lentement, et inexorablement, basculer vers... un peu plus d'ouverture. Pour faire le point et envisager tout ce qu’il reste à faire, voici une rapide rétrospective, une petite revue des pratiques et de l’histoire de l'industrie impitoyable des galettes de silicium.

Il y a 20 ans, j’écrivais « La fabrication d'un circuit intégré entièrement à partir d'outils libres, portables, interchangeables, standard, n'est [...] pas encore possible. » dans GLMF no36 [1]. Que de chemin parcouru depuis ! Pour contempler cette évolution incroyable, nous allons survoler quelques faits marquants, des projets révélateurs et des initiatives aux succès variés. Ne vous inquiétez pas trop des détails techniques : bien qu’il soit question des méthodes de conception et de fabrication d’un circuit intégré, c’est surtout la dynamique de l’industrie qui est au cœur de cet article. La découverte des outils viendra naturellement ensuite !

1. Une longue quête...

La magie de la microélectronique fait rêver d’innombrables bricoleurs : pour beaucoup, le Saint Graal est de créer ses propres puces, et nous allons discuter des contraintes énormes qui confinent cela au domaine du rêve. Il existe pourtant d’autres façons de réaliser des fonctions logiques, par exemple avec des puces programmables [2], mais du fait de son optimisation, rien ne bat une puce « faite maison » concernant :

- la vitesse, en réduisant l’influence des interconnexions ;

- la consommation, puisque sortir les informations d’une puce consomme aujourd’hui la moitié de sa puissance électrique ;

- le coût unitaire, lorsque la puce est fabriquée en masse ;

- la taille, car on ne peut pas faire plus petit ;

- la flexibilité, puisque la puce réalise exactement et uniquement la fonction désirée ;

- la sécurité, car, contrairement à un FPGA par exemple, il est très difficile d'injecter une faille dans une puce que vous concevez à 100 %.

Tous ces avantages sont d’ordre purement industriel, sauf le dernier, qui cristallise depuis plus de deux décennies les angoisses des Libristes, ces personnes qui adhèrent aux idées de la Free Software Foundation. Ils ne cessent d’être échaudés par les innombrables failles et entraves matérielles, comme l’épisode des puces TPM au début des années 2000, les processeurs enfouis tels l’Intel Management Engine ou encore toutes les failles de type SPECTRE. Ces défauts ne sont pas confinés à Intel, ils sont bien symptomatiques de toute l’industrie. Et si les Logiciels Libres sont très actifs sur le front des failles logicielles, ils sont impuissants à remplir cette promesse si la plateforme elle-même a des défauts intrinsèques et irréparables.

Les Libristes sont rejoints de façon moins visible par tous les services chargés de notre sécurité, publics et privés. Ces derniers peuvent mitiger les risques en appliquant des procédures strictes et ils disposent de budgets pour sécuriser leurs plateformes, parfois en commandant du matériel sur mesure. Malheureusement, le grand public se focalise sur le coût d’achat, achète donc son ordinateur en grande surface ou sur Internet, subit la désinformation du marketing et n’influence pas les décisions des concepteurs. L’écrasante majorité des utilisateurs doit se contenter des produits du marché, et les grands fabricants essaient d’écouler un maximum de modèles à bas coût, au détriment de la sécurité.

On dit que « la sécurité est un processus, pas un produit ». Or, toutes les techniques actuelles de sécurisation ne sont que d’innombrables ajouts successifs à une plateforme déjà horriblement complexe, qui s’est développée par accumulation de couches hétéroclites, tout en préservant la sacro-sainte compatibilité avec les versions précédentes. Comment expliquer autrement certaines failles matérielles hallucinantes ?

Ainsi, la course aux améliorations incrémentales, poussée par les pressions concurrentielles du seul rapport performance/prix, a miné le marché des PC et de tous les « gadgets intelligents ». Au final, personne ne peut plus dire comment fonctionne de A à Z cet appareil à 300 €, captif, réduit à la fonction de « terminal de consommation d’informations » irréparable, qu’il faudra jeter une fois qu’un tout petit élément l’empêchera de fonctionner. Le consommateur a abdiqué tous ses « droits à réparer » ce qui lui appartient, alors qu’aujourd’hui l’obsolescence programmée n’est plus une doctrine viable ! Contrairement aux années 70, plus aucun appareil n’est vendu avec une notice technique détaillée, avec schémas et liste des composants, à une époque où se procurer une obscure pièce détachée n’a jamais été aussi facile grâce à Internet.

Une des raisons avancées est le secret industriel. Pourtant, il y a quarante ans, un industriel pouvait demander qu’un circuit intégré soit disponible auprès de plusieurs fondeurs indépendants, pour garantir et sécuriser ses approvisionnements. Grâce à ces licences de fabrication dites « en seconde source », AMD a ainsi conforté le choix d’IBM de doter son PC du 8088 d’Intel. Le succès planétaire de cette plateforme a conduit à une concurrence sans pitié entre les fournisseurs de microprocesseurs, alors que Motorola multipliait les partenariats pour tenter de gagner d’autres marchés.

En 2020, les accords de seconde source sont devenus beaucoup plus rares et les constructeurs de matériel pérenne, pour l’industrie ou la défense par exemple, sont fragilisés. Certains doivent même préserver leur stock de composants critiques dans des armoires réfrigérées, remplies d’azote, durant des décennies. Dans les catalogues des fabricants, les nouvelles références chassent les précédentes au bout de quelques années. De plus, les entreprises peuvent faire faillite ou se faire racheter, donc il est devenu risqué de s’engager sur le long terme dans l’utilisation d’un circuit particulier.

D’autres perspectives inquiétantes étaient déjà visibles à l’horizon depuis longtemps :

- le pistage, comme avec le scandale des numéros de série des Pentium II ;

- l’interdiction de la lecture de certains contenus, tels que les DVD (la saga DeCSS semble déjà oubliée) ;

- la restriction de l’exécution de logiciels, souvent à distance, ce qui se produit aujourd’hui sur votre console de jeux connectée ou votre téléphone mobile sans provoquer d’indignation générale ;

- la limitation du lancement des systèmes d’exploitation libres, sur votre téléphone portable ou votre PC, qui sont pourtant votre propriété, au prétexte que « c’est pour votre sécurité ».

Avec le recul des années, cette dernière mesure apparaît comme l’une des plus efficaces pour endiguer l’adoption des Logiciels Libres par le grand public. L’autre barrière majeure est le refus de documenter la plateforme : fin novembre 2020, Linus Torvalds a annoncé renoncer à utiliser les derniers laptops d’Apple à base de la nouvelle puce M1, puisque Linux ne pourra pas tourner dessus.

Le projet F-CPU, démarré en 1998, avait fait naître beaucoup d’espoirs pour finalement retomber comme un soufflé. Comment ? Pourquoi ? Qui prendra la relève ?

2. Le parcours du combattant du concepteur, d’hier à nos jours

Créer une puce, même si elle n’est pas libre, est une quête louable, à la hauteur des immenses obstacles qui se présentent et qui ne sont pas seulement de nature technique. Imaginons un instant que vous ayez terminé la conception de votre circuit, vous devrez ensuite franchir de nombreuses étapes risquées :

- Pour avoir l'espoir d'un jour signer le contrat et le NDA (accord de non-divulgation très contraignant) avec le fondeur, il faudra d’abord « montrer patte blanche » en raison des restrictions géo-politico-économiques. Alors que les réglementations sur l’exportation des technologies durant la Guerre froide se sont évanouies durant les années 1990, la guerre économique actuelle entre les différents blocs s’amplifie et on parle aujourd’hui de l’émergence du « techno-nationalisme » !

- Puis vous devrez aligner de nombreux zéros sur votre carnet de chèques, quitte à hypothéquer tout le quartier.

- Si vous arrivez jusque là, après la livraison, vous devrez alors tester et encapsuler chaque puce, si elles fonctionnent !

- Reste encore le calvaire de la vente, pour espérer couvrir toutes les dépenses précédentes.

Le bricoleur est donc totalement mis au ban de ce monde.

Malgré les difficultés presque mythiques ou caricaturales que j'évoque ici, il a été possible depuis très longtemps de réaliser des circuits intégrés sur mesure. J'ai bien dit « possible », mais pas « facile », car c'est toujours un compromis entre le coût, la vitesse de réalisation, la performance et la complexité. Pour réaliser des prototypes, les tranches de silicium, aussi appelées « gaufres », sont un coût marginal. Les masques d'insolation sont beaucoup plus chers et il en fallait une demi-douzaine pour réaliser une puce dans les années 70. Ce nombre a régulièrement augmenté depuis, ainsi que leur coût unitaire, et le prix d’un ensemble complet de masques pour une technologie récente est de l’ordre du million de dollars.

Le premier compromis fut de réaliser des puces contenant des transistors prédéfinis, gravés de la même manière pour tout le monde, et le client choisit ensuite les interconnexions pour réaliser les fonctions logiques qu’il désire. Le coût de fabrication est alors réduit à celui d'une puce standardisée sur laquelle il ne reste plus qu'à ajouter une dernière couche métallique pour tracer les pistes, au moyen d'un seul masque au lieu d'une dizaine.

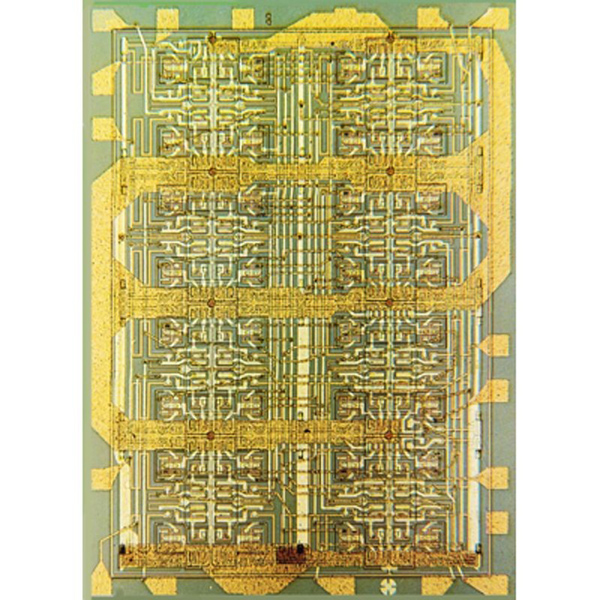

Cette approche économique, appelée « prédifusée », remonte à la fin des années 60 [3]. Ferranti, Fairchild (figure 1), Motorola, Texas Instruments, IBM et d'autres ont conçu des puces capables de réaliser des fonctions logiques arbitraires avec seulement quelques semaines de délai. Leur densité d’intégration a rapidement augmenté et elles se sont retrouvées aussi bien dans de gros ordinateurs que dans nos chers 8 bits mythiques :

- le Sinclair ZX81 emploie une puce appelée ULA pour « Uncommitted Logic Array » [4] ;

- le Commodore 64 contient une PLA (Programmable Logic Array) ;

- l'Amstrad CPC et la famille Thomson MO/TO l'appellent « Gate Array » [5][6].

Au milieu des années 80, on pouvait y caser l'équivalent de centaines de portes logiques qui remplaçaient des dizaines de puces rudimentaires et beaucoup plus encombrantes. L’effet de la miniaturisation est flagrant si l’on compare la taille du Thomson TO7 à celle du MO5, son successeur. Le ZX81 pouvait être encore plus petit, donc encore moins cher !

Cette approche « prédiffusée » existe encore, sous le nom de « Structured ASIC » [7], par exemple pour transférer rapidement des prototypes FPGA sur des puces partiellement préfondues, comme le font eASIC (cette entreprise fut rachetée par Intel) ou le programme Altera HardCopy dans les années 2000 [8] (Altera a aussi été racheté par Intel après lui avoir servi de fondeur). D’autres fabricants existent et cette approche peut réduire le coût unitaire d'un facteur 2 [9] à 5 [8] par rapport au FPGA d'origine, selon le type et les quantités. On trouve aussi un principe similaire, où un canon à électrons grave la couche métallique supérieure d’une puce [10], mais ce procédé est limité aux plus petites séries, car il est beaucoup plus lent.

Les besoins exponentiels de densité et de performance ont éclipsé les circuits prédiffusés au profit d'une approche plus radicale, appelée ASIC. Le terme Application-Specific Integrated Circuit désigne un circuit intégré dont la fonction est dédiée, spécifique au client, et ce dernier contrôle toutes les broches et toutes les couches, non seulement les interconnexions métalliques, mais aussi les transistors. Il est alors seul maître à bord sur le silicium et peut en exploiter toutes les propriétés. C'est beaucoup plus cher, car il faut concevoir et payer tous les masques. L’avantage est que la puce est aussi plus dense : la surface étant utilisée à 100 %, elle est plus performante et plus rentable en très grand volume. Il est aussi possible d’intégrer des circuits spécifiques, comme de la mémoire ou des interfaces analogiques, qui manquaient souvent aux circuits prédiffusés.

Une petite parenthèse s’impose à ce stade : les circuits logiques (re)programmables par l'utilisateur, tels que les GAL, PAL, CPLD et bien sûr FPGA sont apparus un peu plus tard. En plus d'avoir un coût unitaire plus élevé, leur densité et leur performance sont insuffisantes pour les applications les plus excitantes, donc ils ont longtemps été relégués à des fonctions lentes, annexes, aux prototypes ou aux petites séries. De plus, leur utilisation était freinée par le goût des fabricants à faire payer au maximum non seulement les puces, mais aussi les outils de développement, ou à forcer le client à utiliser un système d’exploitation spécifique (et propriétaire, tant qu’à faire). Ces contraintes ont longtemps tenu à l'écart de cette évolution l’amateur comme les logiciels libres...

Pendant ce temps-là, les circuits intégrés continuaient de suivre la loi de Moore vers plus d’intégration, de densité, de vitesse, de fonctions, de glamour même. L'industrie s'est tournée de plus en plus vers la conception d’ASIC à base de portes prédéfinies, afin de réaliser des puces contenant des dizaines ou centaines de milliers de portes logiques, bien plus que ce que les circuits prédiffusés ne permettaient.

Pour y arriver, il a fallu inventer et développer toute une méthodologie ainsi que les outils et logiciels nécessaires. L’idée de base consiste à utiliser des « cellules standard » [11], choisies dans une bibliothèque fournie par le fondeur, afin de réaliser les portes logiques, au lieu de devoir les redessiner à la main, une par une sur des feuilles transparentes, comme à l'époque des pionniers. Leurs formes sont toutes identiques et donc moins optimisées que l'approche manuelle, dite « full-custom », mais ces cellules sont déjà caractérisées (on connaît leurs caractéristiques) et beaucoup plus rapides à mettre en œuvre.

Chaque porte logique est donc vue comme une sorte de brique de LEGO virtuelle, définie et reliée automatiquement par ordinateur. La réalisation d'un circuit intégré à la pointe de la technologie du jour ne demande plus que d'investir dans des ordinateurs énormes, capables de faire tourner des logiciels propriétaires encore plus chers, opérés par des ingénieurs qui ne sont pas non plus gratuits. D’année en année, c'est devenu un modèle économique et industriel viable, en croissance permanente.

3. L’univers impitoyable des fondeurs

L'annonce cet été du projet commun Google/Skywater [12] est un renversement sidérant dans une industrie où la concurrence entre fondeurs est sans pitié. Toutes les étapes de fabrication sont très opaques et les licences concédées aux utilisateurs sont sévèrement restrictives, afin d’éviter toute fuite d'information qui pourrait bénéficier aux concurrents. En effet, fabriquer des semi-conducteurs est un business sans pitié et les fondeurs ne sont pas des philanthropes : ils ont la charge de faire tourner à plein régime leurs usines à 10 milliards de dollars pièce, tout en satisfaisant leurs actionnaires, et ils ne perdent pas leur temps avec de petits clients.

Réaliser une série de puces dans un process ancien coûte déjà des centaines de milliers de dollars et la conception des puces récentes est un investissement chiffré en dizaines ou centaines de millions. C’est une industrie lourde, pas du bricolage. Cela conduit naturellement à regrouper des circuits de prototypes ou des petites séries sur des tranches de silicium partagées entre plusieurs clients : on parle alors de Circuits Multi-Projets (CMP), ou en anglais « Multi-Project Wafer » (abrégé MPW).

Le partage des coûts (surtout la fabrication des masques) est géré par des institutions à l'échelle nationale ou européenne [13]. Les clients sont surtout des startups et des universités, qui sont parfois soutenues par le ministère de l'Éducation ou de l'Industrie de la zone concernée. Aux USA, MOSIS [14] centralise les demandes américaines, alors que le CMP à Grenoble [15] se charge des projets français.

Pour donner un ordre de grandeur, un résident américain doit débourser plus de 10000 dollars pour obtenir une poignée de puces en technologie obsolète (dont certaines dans un boîtier soudable) en passant par MOSIS. Le département du Commerce américain n'autorise pas les étrangers à utiliser ce service, donc les Français doivent s’adresser au CMP [15].

Chaque organisme de partage négocie avec les fonderies participantes pour réserver des gaufres, caler les calendriers, assembler et vérifier la validité des fichiers qui décrivent les dessins des pistes (au format standard GDS), régler les détails administratifs, mais surtout, distribue aussi le précieux sésame qui permet de traduire notre cher circuit abstrait en jolis méandres colorés : le PDK.

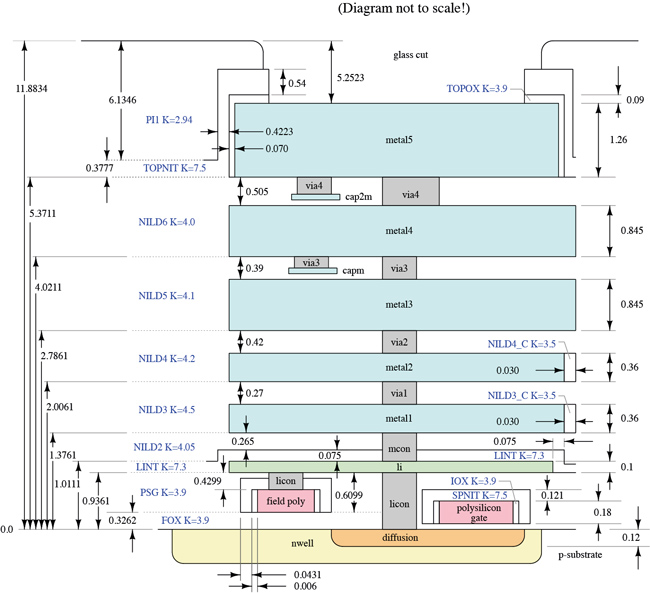

Le Process Design Kit est l’ensemble des informations techniques permettant de dessiner et de fournir des circuits viables sur le process choisi. Cela inclut par exemple des données comme le nombre et les caractéristiques de chaque couche, ainsi que la largeur, l’épaisseur et les espacements permis pour les pistes. Chaque usine a ses propres spécificités et peut fournir différentes options, qui ne sont pas réductibles à un seul nombre comme la largeur de gravure.

Le PDK contient aussi des scripts pour traduire les fichiers, ainsi qu’une collection de composants prédessinés et à placer sur la puce : ce sont les « cellules standard » déjà évoquées. Il ne reste plus qu’à les assembler !

L'encapsulation représente une autre dépense substantielle, car les puces sont normalement livrées « nues », c’est-à-dire que par défaut, seuls de petits rectangles de silicium imprimé seront fournis au client. Chaque exemplaire utilisable du prototype doit être inséré et connecté à un boîtier qui assurera sa protection physique. Cela ajoutera des dizaines ou des centaines de dollars à la facture pour chaque puce, selon le boîtier choisi et le nombre de broches. En moyenne, chaque broche revient à environ 1 $, car les toutes petites séries sont assemblées à la main. Un seul exemplaire d’un petit prototype revient donc à au moins 200 ou 300 $, ce qui ne peut être diminué que par une production de masse.

Même si votre circuit est correct en théorie, il faut aussi s'assurer qu'au moins plusieurs puces du lot n'ont aucun défaut de fabrication. En effet, contrairement à un composant standard, rien ne garantit que la puce livrée fonctionne, à cause de différents types de défauts. Ils dépendent de nombreux facteurs comme la taille de la puce, du nombre de masques, de la position sur la gaufre, etc.

Il vous revient donc de tester méticuleusement chaque exemplaire reçu. Le taux de rejet, ou yield en anglais, peut varier considérablement : entre 5 % et 95 % des puces peuvent fonctionner à la sortie de l’usine. Un fabricant industriel peut affiner ses contrôles de qualité pour améliorer le rendement sur le long terme, ce que l’amateur ne peut pas faire durant le prototypage.

Il existe des équipements spécialisés et hors de prix pour tester une puce directement sur sa gaufre, avant son découpage en petits rectangles. Ces appareils nécessitent une reconfiguration complexe ainsi que de nouvelles sondes pour s’adapter à chaque nouveau modèle de puce. Grâce à ces testeurs automatiques, les industriels n’encapsulent pas les puces mort-nées et réduisent les déchets. Cela optimise les coûts de fabrication en série, puisque l’encapsulation coûte souvent aussi cher que la puce elle-même.

Configurer un testeur de puces et fabriquer la sonde est une nouvelle grosse dépense, il est donc souvent moins cher d’encapsuler directement des prototypes et de prier pour que certains fonctionnent. Il est impossible de souder directement un fil sur une puce, car les zones de connexion, appelée pads, sont espacées d’environ 75 µm seulement. C’est 30 fois plus fin que les broches d’un boîtier classique DIP au pas de 2,54 mm !

Les pads sont reliés aux broches du boîtier par des fils d’or ou d’aluminium lors de l’étape de « bonding ». Cela nécessite encore d’autres appareils sophistiqués qu’il faut aussi programmer. De nouveaux défauts de connexion peuvent apparaître à ce niveau, ce qui affecte encore le yield général.

Enfin, chaque circuit intégré passe sur un banc de test, qui émule parfaitement le système final : la fonctionnalité est intégralement vérifiée dans différentes conditions de température, de tensions, de courants, de fréquence, etc. Cela permet aux fabricants de trier les puces les plus efficaces et de vendre moins cher celles qui ont une unité défectueuse par exemple, sous une autre référence.

Ainsi, un bricoleur doit s'attendre à ce qu’une grande proportion des prototypes qu’il recevra n’ait qu’une qualité décorative...

Alexander a montré sur la figure 2 qu’il n'est pas impossible qu'un particulier fasse fondre sa propre puce, mais ce n'est pas à la portée de tous. Certains passionnés comme Sam Zeloof [16] et Jeri Ellsworth explorent d'ailleurs des méthodes artisanales de lithographie pour réaliser leurs propres semi-conducteurs. Les résultats sont encourageants, mais encore loin d'atteindre une densité et une performance suffisantes pour réaliser un ordinateur, par exemple. Ensuite, il faut choisir : il est difficile de concevoir l'architecture d'un circuit et tous ses logiciels, tout en remplissant son garage de microscopes électroniques, d’acides ultra-toxiques, d'instruments de laboratoire et d’appareils optiques délicats. Nous n’avons qu’une vie et nous ne pouvons pas tout faire en même temps !

Les fonds, les connaissances et les outils doivent donc être réunis et parfaitement maîtrisés pour mener un tel projet à bien. On peut avoir l'un ou l'autre, mais les trois ensemble sont difficiles, ce qui réserve les projets de circuits intégrés à des équipes bien structurées avec une stratégie commerciale bien définie.

Enfin, le plus gros obstacle pour un Libriste est celui des licences. S'il veut réaliser un circuit que d’autres pourront reproduire sans effort, le contrat qu'il signera avec le fondeur le lui interdira ! Toute divulgation des procédés, moyens, fichiers, résultats, qu’ils soient employés, dérivés ou générés, sont des secrets ou de la « propriété industrielle » de l’usine. Malgré les innombrables avancées, une puce totalement libre reste difficile à réaliser dans l'environnement industriel de 2020.

4. ASIC Open Source : une vieille tradition

L'idée de partager les techniques de conception des circuits intégrés n’est pourtant pas nouvelle. La technique des ASIC actuels, consistant à assembler des portes prédéfinies et arrangées par ordinateur, n’a pas eu de succès à ses débuts. Les premiers essais, dont on voit un exemple de 1968 dans la galerie à [3], étaient limités par les capacités informatiques de l’époque.

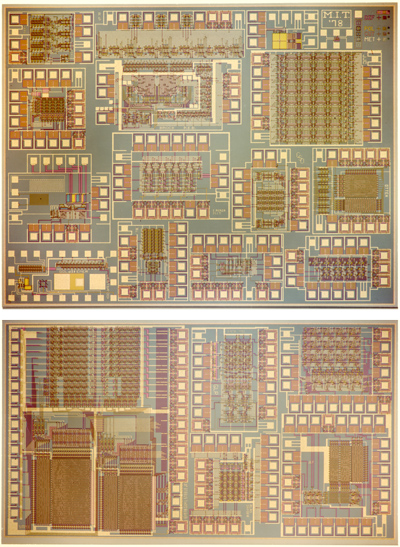

L’idée est revenue en force en 1977 aux États-Unis, lorsque Carver Mead et Lynn Conway [17] ont développé un cursus de conception VLSI, enseigné au MIT à partir de 1978 [18]. Ils ont ainsi réalisé le premier « circuit multi-projets » universitaire (figure 3) et sont à l’origine de l’organisme MOSIS. Les supports de cours se sont rapidement diffusés au-delà du cercle des étudiants, à la manière des sources commentées d'UNIX [19]. Différentes universités se sont organisées grâce à l’interconnexion des établissements par un réseau préfigurant Internet. Cela a révolutionné le milieu universitaire et redéfini l’industrie.

Un peu comme UNIX, cette « méthodologie Mead-Conway » [20] repose sur des principes simples et applicables partout, quel que soit le fondeur. C'est l’idée du plus grand dénominateur commun, une synthèse conservative des contraintes des usines comme des lois de la physique et de la topologie, mise à la portée des étudiants.

Au début, il suffit d’une demi-douzaine de feutres de couleurs, du papier quadrillé, et respecter certaines règles pour obtenir le dessin d’un circuit qui fonctionnera raisonnablement un peu partout. En moins d'une heure, vous pouvez apprendre à dessiner vos premières portes logiques, puis commencer à utiliser un outil de CAO électronique, que les anglophones préfèrent appeler EDA (qui signifie « Electronic Design Automation »).

Les étudiants de Mead & Conway ont appris et affiné les principes de base durant leurs projets d’étudiants, puis chez leurs employeurs, amplifiant ainsi « la révolution VLSI ». Cette dernière commençait à s’essouffler, car à mesure que les procédés de fabrication se sont améliorés, une puce pouvait intégrer de plus en plus de transistors (c’est la fameuse loi de Moore), ce qui a compliqué et a ralenti les projets et a affecté l’industrie tout entière.

- Les premières puces étaient classées dans la catégorie SSI, qui signifie Small Scale Integration. Ils contenaient une douzaine de transistors, par exemple pour réaliser une ou quelques portes logiques. Le circuit 7400, avec 4 portes NAND à 2 entrées, en est un exemple typique.

- Puis la catégorie MSI (pour Medium Scale Integration) a intégré une centaine de transistors et a permis des fonctions plus complexes comme des compteurs ou des petites mémoires. On a ainsi pu fabriquer des fonctions arithmétiques (tel le 74181), des registres à décalage complexes comme le 74595, ou même des interfaces séries asynchrones (UART) sur une seule puce.

- Dans les années 70, la catégorie LSI (Large Scale Integration) a permis de réaliser les premiers microprocesseurs, comme les mythiques 8085, 6800, 6502, Z80 et de nombreux autres. Des milliers de transistors sont toujours dessinés à la main sur une demi-douzaine de grandes feuilles transparentes. C’est une méthode délicate, car la moindre erreur est catastrophique et se cache facilement.

- L’échelle VLSI (Very Large Scale Integration) n’était plus réalisable à la main que par les plus grosses équipes industrielles. Intel ou Motorola pouvaient allouer des dizaines d’ingénieurs à la conception du 8086 ou du 68000 (respectivement 29000 et 68000 transistors), mais le facteur humain limitait sérieusement la croissance de la complexité et de la performance des circuits intégrés.

L’informatisation de nombreuses étapes de conception, de vérification et de test, ainsi que l’arrivée de nouvelles générations d’ordinateurs, a repoussé les limites de la complexité et permis de créer des puces, donc des ordinateurs, encore plus puissants, avec moins de personnel. Par exemple, la puce du Propeller II de Parallax est conçue par un seul ingénieur, avec l’assistance ponctuelle du fondeur. De l’autre côté du spectre, le Xilinx Virtex UltraScale+ VU19P intègre 35 milliards de transistors (un million de fois plus que le 8086) alors que le développement des logiciels associés occupe plus de personnes que la conception de la puce.

De nombreuses sociétés ont été créées ou ont bénéficié de cette nouvelle vague et l'industrie s'est restructurée. La conception d’une puce n'est plus intimement liée au fondeur et les équipes de conception des circuits se sont progressivement dissociées des usines. De nombreuses sociétés « sans usine », ou « fabless » dans le jargon, ont éclos, telles ARM ou eASIC citées précédemment. Elles font sous-traiter la fabrication à d’autres sociétés, les « fondeurs » comme TSMC, Samsung, UMC, Global Foundries, Skywater, STMicroelectronics, et beaucoup d’autres [21].

Le grand bénéficiaire actuel de ce mouvement est ARM, qui vend des licences pour ses circuits à toute usine en mesure de fondre une porte logique. De l’autre côté, Intel est l’un des derniers fabricants « monolithiques », c’est-à-dire qu’il dessine et fabrique tout de A à Z. Il est pourtant forcé de s’ouvrir depuis quelques années, aussi bien pour faire sous-traiter par TSMC des puces qu’il n’arrive pas à produire correctement lui-même, que pour sous-traiter la production d’autres concepteurs « fabless » afin de faire fonctionner et rentabiliser ses vieilles lignes de production encore un peu.

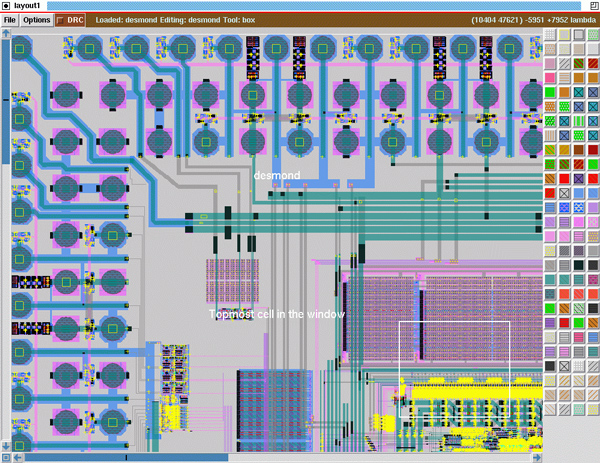

Les logiciels propriétaires, conçus par Synopsis, Cadence, Mentor Graphics, etc. ont bien sûr mené la danse, mais il existe aussi l'outil Magic [22] depuis 1983. C’est un éditeur graphique (figure 5) diffusé sous licence BSD qui continue d'être activement développé. D'une taille modeste, porté sur UNIX/Linux et Windows, il reste simple d'utilisation, tout en étant d'une grande flexibilité grâce à son langage de script tcl. Magic permet ainsi aux universités d'expérimenter et de bricoler de nouvelles idées, en allouant les budgets à la fabrication des puces au lieu de licences EDA. Un logiciel similaire totalement libre est GNU electric.

5. Des projets libres

Les NDA, les budgets et de nombreuses autres limitations ont donc longtemps relégué les bricoleurs ambitieux à des descriptions de haut niveau, en Verilog et VHDL essentiellement. C'est ainsi que le projet F-CPU (Freedom CPU Project) a démarré en 1998 [23] sous l'impulsion de trois Linuxiens. Ils furent vite rejoints par des dizaines de passionnés suite aux échos sur les sites web de nerds [24]. L'engouement général a même porté l'équipe jusqu'à présenter le projet dans des conférences, dont quatre fois au CCC à Berlin de 1999 [25] à 2002.

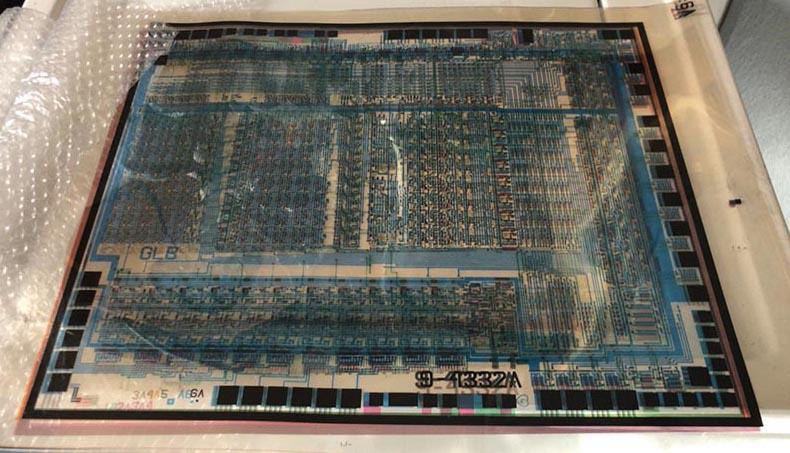

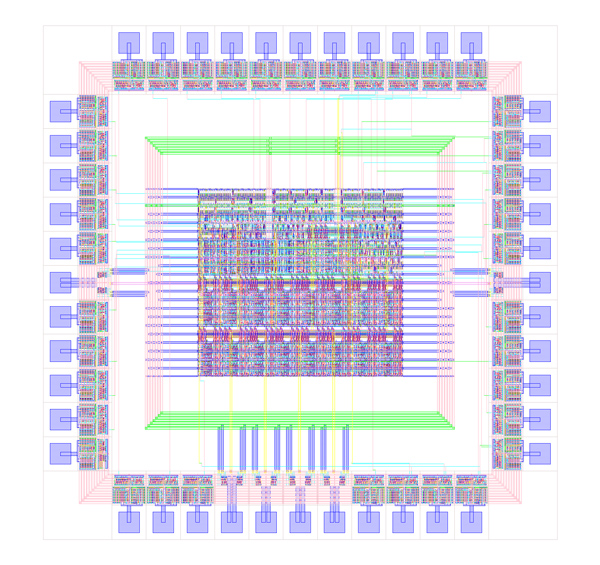

Imaginer une architecture idéale est facile, mais la réaliser est une autre histoire. Faire de jolis diagrammes ne suffit pas : il faut décrire, donc écrire le circuit en VHDL, puis le simuler. Devant le manque criant d'outils libres et de méthodes répondant à l’éthique des Logiciels Libres, il a fallu étudier les différentes possibilités et essayer les outils disponibles [26]. Parmi ceux-ci, Alliance [27] avait été créé au début des années 90, il permettait de réaliser des puces avec 10000 portes logiques (comme celle de la figure 6) et était libre. Cependant il était lourd, complexe et surtout les fichiers utilisaient des sous-ensembles de VHDL qui n'étaient pas vraiment conformes aux standards ou aux principes mêmes du langage VHDL, donc limitants et non portables. Heureusement, la situation a évolué dans le bon sens depuis 20 ans.

D’autres logiciels du marché ont été testés, comme ncvhdl, Simili, Vanilla VHDL, Aldec Riviera et modelsim. Ce n’était pas la panacée :

- Tous étaient propriétaires ou non libres.

- Certains outils étaient gratuits et un peu limités.

- D'autres nécessitent des licences payantes, dont certaines ont été gracieusement fournies pour évaluation.

- Windows était encore hégémonique dans l’industrie à l'époque, et Linux n'était pas encore la plateforme reconnue des développeurs, ce qui empêchait une utilisation vraiment libre des outils.

Les outils ainsi que les méthodes de conception et de simulation du F-CPU ont été publiés dans GNU/Linux Magazine no36 [1].

GHDL [28], écrit en Ada et reposant sur GCC ou LLVM, n'est arrivé que des années plus tard et le projet F-CPU était déjà oublié en 2010 [29] lorsque GHDL a enfin mis fin au supplice de devoir tester chaque fichier sur de multiples outils1. En effet, il fallait constamment s'assurer de la compatibilité du code source et contourner les défauts et limites de chaque outil. À un moment, il faut choisir entre développer et se battre contre ses propres outils...

Par manque de moyens, de contributeurs qualifiés et de temps, le projet s'est ainsi lentement évaporé, mais de nombreuses alternatives apparaissaient à la même époque, alors que tout le monde surfait allègrement sur la Grande Vague d'Internet. Le site OpenCollector.org [30], clos en 2014, collectait des liens vers les différents projets de matériels et de conceptions libres ou gratuites. Des webrings comme « Utopia Computing » [31] ou « Homebrew Computers Web-Ring » [32] réunissaient les hobbyistes de tous bords. Usenet n'était pas encore bloqué par les ISP et permettait à n'importe qui d'échanger librement ses idées sur les groupes comp.arch ou comp.lang.vhdl...

De nombreux projets ont essayé d'émuler le succès grandissant de Linux et des Logiciels Libres pour l'appliquer plus ou moins directement au matériel, avec des résultats mitigés. Qui se souvient par exemple de OpenIPCores, OpenHardware.de, OpenTech CDROM ou même OSCAR2 ?

C'est aussi autour de l'an 2000 que les questions concernant les licences gouvernant les circuits numériques ont enfin été abordées sérieusement, calquant les modèles logiciels.

- D'un côté du spectre, le projet F-CPU avait une attitude libriste jusqu'au-boutiste, c'est-à-dire qu'il fallait libérer aussi bien le processeur que les outils de conception, de bout en bout, afin qu'absolument n'importe qui puisse réaliser sa propre version.

- De l'autre côté, les industriels rêvaient de pouvoir utiliser gratuitement et sans aucune contrainte le travail collectif des bricoleurs. Un jour, l’équipe du F-CPU fut même approchée par une grosse société pour « collaborer », sans chercher à contribuer le moins du monde au projet : cette société semblait seulement intéressée par les talents et la communauté de développeurs pour renforcer sa base d'utilisateurs.

On retrouve encore aujourd'hui les mêmes discussions sur les défauts et forces des licences GPL, LGPL, AGPL, BSD, Apache, Mozilla Public License (MPL) ou Creative Commons, auxquelles se sont ajoutées des licences plus spécifiques [33] comme la CERN Open Hardware License (CERN OHL) ou la TAPR Open Hardware License (TAPR OHL) pour ne citer qu'elles. Le choix est fabuleux, sauf quand il y en a trop. Il y en a même tellement que l'on s'y perd et on préfère trop souvent créer sa propre licence, pour être bien sûr que la vision personnelle de l'auteur est correctement exprimée. Cette confusion mène à la fragmentation, puis la dilution des efforts de toute la communauté...

La question stratégique du « Libre contre ouvert » n'est pas non plus innocente dans le domaine du matériel [34]. Les points de vue des acteurs divergent toujours sur un point ou un autre, et les organisations et fondations se sont aussi multipliées, chacune de leur côté, alors qu’aucune ne semble directement affiliée à la FSF :

- Open Source Hardware Association (oshwa.org) ;

- Open Design Foundation ;

- FreeIO (http://freeio.org/) ;

- Open Hardware Foundation ;

- Openhwgroup.org ;

- Openhardware.org ;

- Free Hardware Designs (fhwd.org) ;

- The Free and Open Source Silicon Foundation (https://fossi-foundation.org/)...

On a aussi vu apparaître l'« openwashing » : cela consiste à coller le préfixe « open » sur des mots courants pour recycler les tendances, surfer sur la vague, redéfinir les marchés et conquérir le futur. Par exemple, IBM ajoutant le préfixe e- et Apple le préfixe i- sur tout ce qui bougeait. Des sociétés et cartels se sont aussi constitués pour suivre le mouvement et mettre leur propre personnel à la tête des comités et fondations, de la même manière que cela se produit dans le monde logiciel ou les comités de normalisation.

Richard Stallman a attendu 2015 [35] pour comprendre les implications de ce foisonnement qui a empêché une unification des licences et donc la cohésion de tous les projets, enfermés dans leurs petits silos incompatibles. Il faut admettre que la terminologie anglaise « Free Hardware » est ambiguë et facile à méprendre pour « matériel gratuit », ce qui n'est pas du tout l'intention. C’est même plus grave que pour le logiciel, qui lui peut être dupliqué gratuitement. L'attribut Libre est donc préféré pour montrer une adhésion aux idéaux de la FSF. La GNU GPL s’est adaptée pour que sa v3 s'applique aussi à des conceptions matérielles et le degré de licence Copyleft à adopter reste un choix de l'auteur.

Des projets ont eu un certain succès, par une approche que l'on peut qualifier de pragmatique, et ils ont même changé la donne dans leurs domaines respectifs : par exemple, les imprimantes 3D ou la plateforme Arduino, puis le Raspberry Pi se sont basés sur l'idée d'ouverture comme business model. Le succès attire les imitations, les clones et même les innovations, ce qui enrichit ces pages ainsi que le monde des bricoleurs depuis des années. Mais l’ouverture n’est pas la liberté. Le code source n’est que la surface de l’iceberg.

Une autre initiative ouverte est apparue presque en même temps que le projet F-CPU : le site OpenCores [36] s'est ouvert en 1999 avec pour ambition de réunir autant de codes sources HDL (appelées « IP cores » pour faire trendy) gratuits que possible. Cependant, la publicité sur le site ainsi que la nécessité de créer un compte pour pouvoir télécharger les fichiers trahissaient l'ambition commerciale de l'équipe. Les habitués des logiciels libres n’ont pas pour habitude de s’inscrire pour installer un logiciel et il aurait été plus éthique que le site utilise l'extension .com au lieu de .org.

Le site a réussi à fédérer de nombreuses contributions et à accumuler des centaines de projets. L'équipe a aussi lancé son propre projet de processeur appelé OpenRISC 1000 [37], écrit en Verilog. Son architecture reprend trait pour trait les concepts des livres de Patterson & Hennessy et ressemble donc énormément à un cœur MIPS canonique. Cela lui a permis d'obtenir très rapidement le support de GCC et ainsi de faire tourner Linux avec peu d'efforts.

Après avoir tourné sur des FPGA, plusieurs réalisations en silicium du cœur OR1K ont vu le jour avec des partenaires industriels de ORSoC.se, la société qui maintient OpenCores.org depuis 2007. Le processeur est intégré dans quelques produits industriels ou grand public, mais pour l'instant, aucune puce réellement libre n'a été réalisée et on ne trouve pas encore de linuxette basée sur OpenRISC, suite à l'échec d'une opération de crowdfunding en 2017 [38].

En 2015, alors qu'ORSoC AB surfait sur la vague juteuse des ASIC de cryptomining, les utilisateurs délaissés de OpenCores.org ont créé LibreCores.org et établi FOSSi, la « Free and Open Source Silicon Foundation », pour s’affranchir de toute dépendance commerciale. Mais c'était trop tard, car GitHub, Open Hardware Repository [39], Hackaday.io et plein d'autres sites communautaires saturaient déjà l'offre d'hébergement gratuit de projets libres. OpenCores.org continue au ralenti et profite de l'inertie de son nom. De son côté, la FOSSi est aujourd’hui une partenaire importante dans l’initiative Google/Skywater.

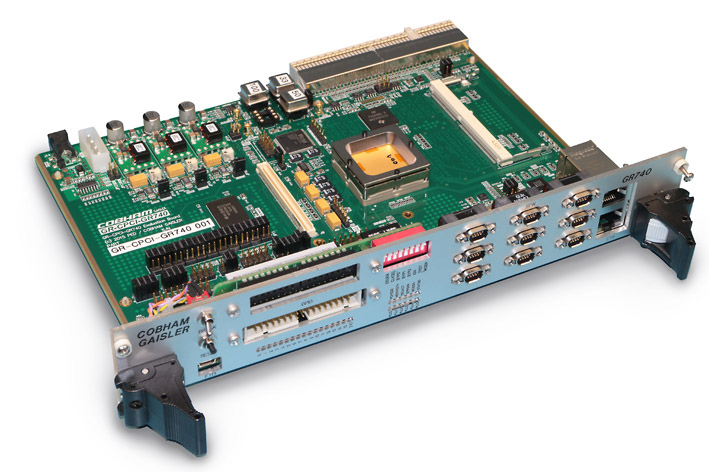

Un processeur vraiment libre, vraiment bien fait, vraiment utilisé est le LEON [40] (figure 7) conçu par Jiri Gaisler pour l'ESA à partir de 1997. Ce cœur compatible SPARC V-8 est écrit en VHDL et est disponible à la fois sous licence LGPL et GPL. Il s'est retrouvé embarqué dans de nombreuses puces spatiales tolérantes aux radiations, comme la sonde Solar Orbiter lancée en février 2020 qui en contient 9 [41]. Le LEON a aussi été adopté dans des produits grand public, tel un NAS utilisant un SoC IT3107 d'Infrant Technologies, décrit dans GNU/Linux Magazine [42].

Aujourd'hui, le site qui héberge les développements du LEON montre que la société de consulting Gaisler Research de Jiri a été intégrée dans la société Cobham. Les différents cœurs LEON continuent d'être utilisés un peu partout, dans l'industrie comme dans la recherche, grâce à son code soigné et flexible. D’ailleurs, cela fait de ce projet une référence appropriée pour tester de nouveaux outils ou techniques, comme l’efficacité d’un simulateur ou la conformité d’un synthétiseur : bien que l’architecture SPARC soit un peu passée de mode, elle ne risque plus d’évoluer et la stabilité rassure les industriels.

6. Des projets libérés

Sun Microsystems a suivi la tendance en publiant en 2006 le code source de son dernier processeur 64 bits UltraSPARC T1, avant de se faire avaler par Oracle. Renommé OpenSPARC T1 [43], c'est un réel processeur propriétaire qui a été libéré sous licence GPL, comme son successeur l'OpenSPARC T2 à la fin 2007. Il faut croire que Jiri leur avait déjà coupé l'herbe sous le pied, car l'opération ne semble pas avoir eu d'impact particulier, à part une version chinoise destinée à un superordinateur expérimental [44]. La réticence d'Oracle de continuer d'investir sérieusement dans l’héritage de SUN n'a pas non plus beaucoup aidé. Cela montre une fois de plus qu’un projet dépend d’innombrables facteurs, outils et contraintes, et que « le code source seul ne suffit pas ».

Pour continuer dans la série openwashing, tournons-nous maintenant vers IBM qui a méticuleusement ouvert son architecture POWER pour créer, roulements de tambour... OpenPOWER [45] en 2013 ! Ici, il ne s'agit pas juste de coller une étiquette GPL sur une archive de code HDL avant de tourner les talons, mais de créer un organisme pour fédérer une communauté : l'OpenPOWER Foundation [46] qui remplace POWER.org, le rôle de ce dernier étant déjà de gérer les spécifications du jeu d'instructions. Malgré l’abandon des processeurs PowerPC par Apple, l'impact est plus important que pour OpenSPARC, du fait des nombreuses applications de l'architecture dans d’autres domaines de niche, comme les SoC pour contrôle embarqué, l’industrie réseaux/télécoms, les superordinateurs... Et bien sûr les consoles de jeu, dont l'inoubliable Cell [47] de la PS3 de Sony.

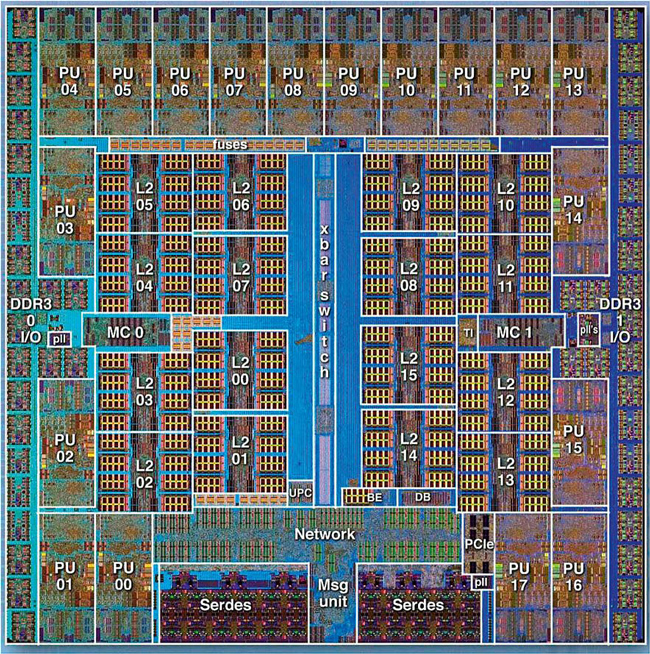

Depuis 2019, la fondation a publié deux implémentations de référence de la dernière révision de l'ISA : Microwatt et Chiselwatt [48], écrits respectivement en VHDL et en Chisel. Ces deux projets n'ont pas encore été réalisés sur du silicium et servent pour expérimenter sur des FPGA, par exemple. Plus récemment, la publication des cœurs A2I et A2O [49] sous licence Creative Commons sur GitHub [50] relance la course à la performance et offre une alternative à l'énorme OpenSPARC T2. Il s’agit ici d'un processeur conçu initialement pour les consoles de jeux vidéos et qui constitue la base de plusieurs superordinateurs (figure 8) comme le BlueGene/Q [51], que l'on trouvait en haut du classement TOP500 autour de 2010. Cependant, ces cœurs ne sont pas de toute première fraîcheur et ils n'ont pas encore été mis à jour pour adhérer aux spécifications actuelles : ils supportent l'ISA 2.07 alors que la version 3.1 est arrivée.

On garde IBM sous le coude pour plus tard et on passe aux « softcores propriétaires » : ce sont des modules précompilés et optimisés pour utiliser un FPGA particulier, qui sont souvent distribués par le fabricant sous forme binaire ou opaque. Il existe toutes sortes de circuits « prêts à intégrer » comme des interfaces de communication (série, SPI, I²C, mémoire dynamique, contrôleur d’interruptions…), mais nous allons nous pencher sur les microprocesseurs : les NIOS & NIOS II d'Altera, le Microblaze de Xilinx, ainsi que le LatticeMico32. Ils ont été créés par les fabricants de FPGA respectifs pour faciliter la vie de leurs clients, qui bénéficient régulièrement de puces de plus en plus larges, et sont constamment tentés d’embarquer un processeur de contrôle. La fourniture de code « prêt à intégrer » propriétaire est une façon de garder les développeurs captifs d’une plateforme.

Les NIOS et Microblaze sont arrivés en premier et souffrent donc d'un défaut majeur : leur licence autorise leur utilisation uniquement sur les puces fabriquées par leur auteur. Avec la course à l'intégration, on a vu apparaître chez Xilinx des cœurs PowerPC « en dur », c’est à dire directement intégrés sur la puce, donc non reconfigurables, plus performants et compacts. Cependant, pour faciliter la transition des clients, les fabricants ont fini par adopter les cœurs ARM Cortex, d’abord en « softcore » puis en « hard macro » (une autre façon de dire « en dur »).

Aujourd'hui, ce sont les cœurs RISC-V qui ont le vent en poupe : MicroSemi est le pionnier, avec son FPGA PolarFire [52] conçu après avoir ingéré Actel et avant de se faire avaler par Microchip.

Le LatticeMico32 est arrivé après les NIOS et Microblaze, en 2006. Sans la restriction de plateforme [53], il a conquis plus d'utilisateurs et est notoirement à la base en 2010 du projet MilkyMist de Sébastien Bourdeauduc. Ce dernier a ensuite essaimé d'autres projets au sein de M-Labs, puis ARTIQ. Par exemple, Sébastien est aussi le créateur de Migen, puis son reboot nMigen, un « métalangage » basé sur Python pour décrire du matériel de façon plus abstraite que le Verilog. L’apprentissage du VHDL étant plus compliqué, la mode est aux métalangages : MyHDL utilise aussi Python pour décrire des circuits de haut niveau, alors que SpinalHDL et Chisel sont basés sur Scala.

Le tour d’horizon est presque fini et il ne reste plus que quelques tristes sires à mentionner.

- D'abord Intel qui, suite aux difficultés et retards pour exploiter ses usines de toute dernière génération, se retrouve obligé d'apprendre à s'ouvrir un peu (et freiner sa manie de racheter à tour de bras) s'il ne veut pas que son modèle d'intégration verticale, qui consiste à tout faire en interne, continue de s'effondrer devant les limites de la loi de Moore. Chaque nouvelle usine coûte de plus en plus cher et si elle fonctionne mal, on peut comprendre que les actionnaires se fâchent.

- Ensuite ARM qui continue de passer de mains en mains et perd son statut de « Suisse de la microélectronique » avec son rachat par NVIDIA.

D’ailleurs, ARM comme Intel ne lâcheront jamais quoi que ce soit d’important sous licence libre. Tel Microsoft qui fut effrayé par Linux, ils n'hésiteront pas non plus à user des mêmes tactiques : « embrace and extend » et FUD. ARM a d’ailleurs lancé une campagne de marketing en 2018 pour s'attaquer à RISC-V [54] en créant le défunt site https://riscv-basics.com, mais cette initiative s’est vite retournée contre ARM.

- MIPS (ou ce qu'il en reste après plusieurs rachats et démembrements) a bien essayé de faire un « programme d'accès facile » imitant le DesignStart d'ARM [55], mais personne, à part les clients déjà captifs, n'est dupe et ces initiatives ne rivalisent pas avec les avantages particuliers des cœurs « open source ».

- Tout cela ne fait que renforcer le cartel RISC-V dont la licence permissive permet aux gros utilisateurs comme Western Digital de pomper allègrement non seulement le cœur, mais aussi tous les outils de développement, afin de réaliser des économies énormes, puisqu’il n’est plus obligé de payer les redevances à ARM pour chaque disque dur vendu. Grâce à l’Open Source, WD peut maintenir l'opacité de ses produits sans tout reverser à la communauté, à part un dépôt Git partiel et l'annuité pour garder son siège au comité de direction. Qui ne l'a pas vu venir ?

Pour en revenir aux projets libres qui ont abouti, on voit encore que tous ont dû s'appuyer sur des connaissances partielles de la technologie cible, que ce soit du FPGA ou du silicium, ou alors il a fallu signer des NDA. La mise en garde (traduite de l'anglais) en bas de la page principale du projet Coriolis [27] ne peut pas être plus claire :

« Actuellement, les outils Alliance / Coriolis ne sont pas adaptés à des finesses en dessous de 130 nm. Pour préserver la portabilité entre les fonderies et rester indépendant de leurs NDA, Alliance / Coriolis repose sur un système portable, ou symbolique. Pour produire votre propre ficher GDS, vous devrez utiliser l'outil de traduction s2r qui nécessite un fichier de configuration spécifique à la technologie cible, qui est sous NDA. Ainsi il doit être soit écrit par vous-même ou bien fourni par un service tel que MyCMP [15]. »

Dans d'autres cas, comme pour OpenRISC ou LEON, le cœur a été fabriqué par d'autres équipes que les concepteurs d'origine, ce qui court-circuite la question des NDA sans apporter la moindre contribution en retour au projet.

7. 2020 : la nouvelle vague

De nombreux acteurs se sont donc investis depuis des années dans le domaine du matériel ouvert ou libre, parfois avec succès. Ce sont des universités, des entreprises privées nouvelles ou établies, ainsi que des amateurs avec différents degrés d’organisation. Les projets « ouverts » ou « libres » ont rarement un impact important sur l’industrie et n’entrent pas vraiment en concurrence avec les grands fabricants. Ces derniers les ignorent souvent, à l’exception de ARM comme mentionné plus haut, et on doute que cette erreur se reproduise de si tôt.

L’ouverture invite à la collaboration et malgré la tendance habituelle de chacun à vouloir faire selon nos propres envies (ce sera forcément mieux que ce que tous les autres ont déjà fait, n’est-ce pas ?), le mouvement prend de l’ampleur et mûrit doucement. Les projets qui ont échoué ont servi de leçon à la communauté, qui s’agrandit à mesure que les débutants débarquent et prennent le relais. Les plus jeunes ont naturellement l’habitude de collaborer sur Internet et bénéficient pleinement des résultats de tous les projets libres précurseurs. Par exemple, Linux a remplacé Windows comme la plateforme de référence, au point que Microsoft intègre de plus en plus le premier au deuxième. Quel revirement pour Steve Ballmer !

Des liens se sont progressivement noués entre institutions, organismes, sociétés et particuliers, autour d’objectifs communs. C’est là que nous faisons connaissance avec un autre acteur qui va cristalliser la fin de cet article et réunir une partie des organisations présentées dans les chapitres précédents.

NLnet [56] est un pionnier néerlandais historique de l’Internet qui, suite à la vente de son activité d’opérateur en 1997, est devenu une fondation qui milite activement pour renforcer les libertés sur le réseau mondial. « Fix the Internet » (réparer l’Internet) est son credo, et son arme est l’argent : il redistribue une partie des fonds perçus lors de la vente de sa filiale, et accepte aujourd’hui les dons des particuliers et des entreprises. Aujourd’hui, la fondation est une interface entre les développeurs et les aides de l’Union européenne ou les dotations de dizaines d’autres fondations, afin de soutenir de nombreux projets comme Tor, Jitsi, WireGuard, NoScript, GPLv3...

N’importe qui ayant une adresse de résidence en Europe peut déposer un dossier pour présenter son projet [57] et demander une aide financière non imposable. En retour, les projets retenus doivent être organisés de façon totalement transparente, parfaitement auditable, capable de justifier toutes les décisions. Cela exclut donc les projets faisant appel à des accords secrets ou des discussions non publiques.

Les projets retenus sont donc dans la droite ligne de l’esprit de la Free Software Foundation, mais comme vous le savez peut-être, « il ne peut y avoir de logiciel libre sans matériel libre ». Justement, nous allons finalement parler d’un projet ambitieux, mais toujours cruellement nécessaire qui vise à réaliser un processeur complètement libre, 20 ans après le F-CPU...

8. De Libre-RISCV à Libre-SOC

Il s’agit du projet Libre-SOC [58] qui a été lancé en 2018 lors d’une campagne de financement participatif [59][60] par Luke Kenneth Casson Leighton. Dans les années 90, Luke fut l’un des contributeurs de SAMBA, donc expert de l’ingénierie inverse des systèmes propriétaires et témoin de leur impact négatif sur les logiciels libres. Puis il s’est investi dans le projet EOMA68 [61] visant à créer une plateforme matérielle totalement libre : ce serait un ordinateur que chacun pourrait réparer ou bricoler. Il a donc acquis une certaine expérience dans les rouages de la conception et la fabrication de cartes électroniques, et les solutions disponibles sur le marché ont créé d’innombrables frustrations.

À la longue s’est imposé le besoin d’un processeur exempt de tout secret industriel. La question des licences était centrale dès le début et la seule façon d’y arriver est finalement de réaliser soi-même la puce. Le choix de la licence LGPLv3+ (similaire au LEON) s’explique par une stratégie de licence double, similaire au LEON :

Naturellement, Luke s’est tourné vers l’écosystème RISC-V pour trouver des ressources, dont un jeu d’instructions peaufiné, à partir duquel il pourrait concevoir un processeur adapté à ses besoins : embarquable, avec une consommation modeste, capable de faire fonctionner une tablette, par exemple.

L’architecture de Luke apporte la particularité de fusionner le processeur central avec l’accélérateur graphique. Le but n’est pas de concurrencer les leaders du marché, car ils ont accès aux technologies les plus récentes pour optimiser la consommation et la performance. La stratégie est de viser les marchés émergents ou futurs, avec l’ambition de créer de nouvelles générations d’ordinateurs personnels « éthiques ».

En observant les systèmes récents, on s’aperçoit que les coûts de la communication entre le processeur central et le processeur graphique ont explosé : d’innombrables bus intermédiaires et couches logicielles se sont interposés entre l’algorithme de l’utilisateur et sa réalisation effective. Avec le temps, envoyer des commandes ou des données est de plus en plus complexe, prend plus de temps, donc consomme plus d’énergie et dilapide les transistors. Un cœur de processeur adapté pour réaliser aussi les opérations graphiques les plus courantes est un compromis intéressant, à mi-chemin entre un cœur classique et un duo CPU-GPU. Cette approche semble la plus favorable lorsqu’une technologie de silicium un peu ancienne doit limiter sa dissipation au maximum.

En se basant sur le modèle de programmation du RISC-V, Luke a conçu une version vectorisée du jeu d’instructions ainsi qu’une microarchitecture dérivée des principes du vénérable CDC6600 [63] grâce à la participation de Mitch Alsup. Ce dernier a été l’architecte de la famille RISC MC88000 chez Motorola, puis des processeurs compatibles SPARC V-8 chez Ross et du K9 chez AMD, pour ne citer que les plus connus ! Mitch a aussi aidé à concevoir les unités de virgule flottante et en particulier celles de calcul transcendantal (trigonométrie, division, racine carrée...).

9. Une organisation ouverte et innovante

En 2019, les bases de l’architecture se sont posées et précisées, et le projet s’est organisé autour des contributeurs grâce à une mailing list publique [64] où chacun expose ses activités quotidiennes avec un « daily kan-ban ». Plusieurs demandes de soutien ont été envoyées à NLnet et certaines ont été acceptées [65]. Ce sont autant de budgets de 50000 € chacun à gérer méticuleusement.

Les tâches sont attribuées à chacun selon la disponibilité et les domaines d’expertise : pile des logiciels graphiques, conception de la puce, adaptation des différents outils... L’avancement est tenu à jour sur le bugtracker du projet [66] afin de garantir que chaque participant soit rémunéré en proportion de ses contributions. C’est aussi un élément d’audit critique pour NLnet, puisque la fondation ne libérera les fonds qu’une fois tous les objectifs remplis !

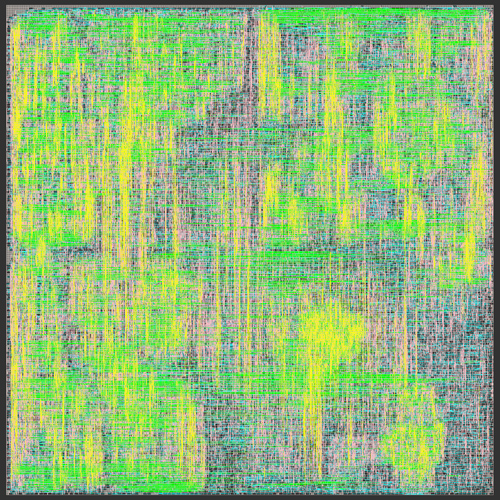

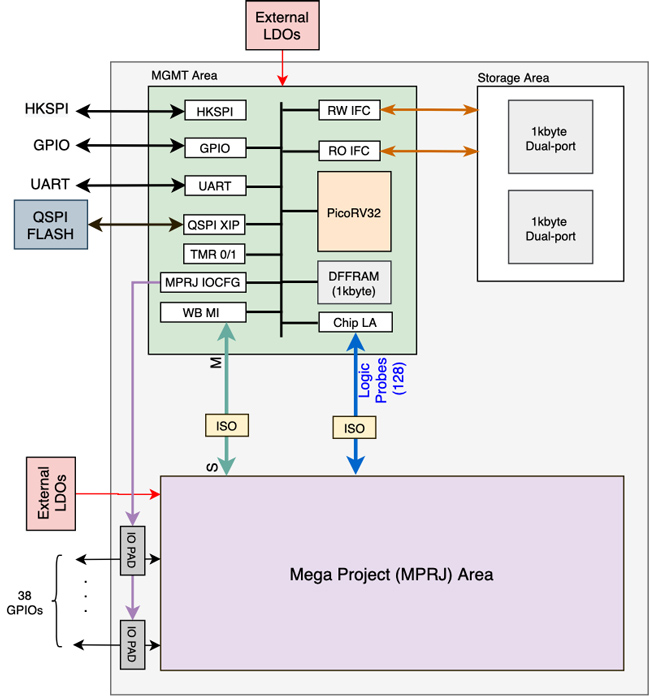

NLnet finance aussi la fabrication d’un prototype partiel, prévu pour être fondu par Europractice à partir de décembre 2020. Pour cela, la fondation rémunère directement Chips4Makers [67], une petite société qui fait l’interface entre des projets libres et des fondeurs, à la façon de CMP, mais isolant le projet libre des contraintes de NDA et de PDK. Ce prototype validera les outils, l’organisation, les procédures et l’architecture de base, ce sera donc loin d’être la puce performante que vous pourrez acheter et utiliser. En effet, la technologie choisie pour l’essai est en 180 nm et la surface est estimée à seulement 20 mm² (voir la figure 9). C’est le moins risqué et le moins cher pour fondre une centaine d’exemplaires seulement. Ce choix limite par contre la complexité de la puce, qui n’aura que peu de mémoire cache, par exemple. Mais il faut bien commencer quelque part et si tout va bien, la prochaine étape sera de descendre à 45 nm vers 2022.

Les circuits sont décrits en Python avec nMigen, ce qui génère ensuite du code Verilog qui sera ensuite synthétisé, puis placé-routé avec la suite Coriolis, le successeur d’Alliance. Le projet Libre-SOC pousse nMigen et Coriolis dans leurs retranchements et la collaboration permet aussi à ces outils de s’améliorer, grâce à des rapports de bugs ou la mise au point de fonctionnalités nouvelles qui profitent à tout le monde.

Les premières simulations commençaient à fonctionner lorsque Luke a dû se rendre à l’évidence que la fondation RISC-V n’accepterait jamais de négocier ouvertement sur l’ajout de son extension vectorielle au jeu d’instruction3. Après 18 mois de développement autour de RISC-V, il fallait remettre tout à plat et sélectionner soigneusement une alternative [68]. C’est paradoxalement la fondation OpenPOWER qui a débloqué la situation grâce à son ouverture et des interlocuteurs attentifs [69]. L’architecture POWER est considérablement plus complexe et alambiquée que RISC-V et la modification du code source a pris des mois, mais le nouveau code a commencé à fonctionner sur un FPGA en septembre 2020 [70]. Il a aussi fallu renommer tout le projet, de Libre-RISC-V à Libre-SOC, et changer de nom de domaine !

Beaucoup de personnes sont en droit de douter de ce projet et les raisons ne manquent pas. Le report de la fabrication de la puce d’octobre à décembre 2020 attire déjà des rires moqueurs, mais en regardant de près, on voit qu’au-delà de la poignée de contributeurs expérimentés au cœur du projet, ce dernier a su tisser des liens fructueux avec d’autres projets et des organisations cruciales pour atteindre les objectifs. Google pourrait même un jour allouer de la place à Libre-SOC dans son programme de prototypes gratuits, mais il est encore trop tôt pour y songer.

Nous sommes bien loin de l’aventure du projet F-CPU qui s’est déroulée exactement 20 ans plus tôt, car malgré les très nombreux parallèles qui provoquent un intense sentiment de « déjà vu », cela fait chaud au cœur de voir que beaucoup de problèmes fondamentaux ont été résolus durant les deux dernières décennies. Le F-CPU manquait cruellement d’expérience, de soutien financier sérieux, d’outils, et ce n’est plus qu’un lointain souvenir. C’est même une page que l’on peut enfin refermer, maintenant que la relève est là. Et pour ceux que l’ISA de POWER rebute, Libre-SOC pourrait aussi devenir une plateforme pour expérimenter de nouveaux jeux d’instructions, puisque le code source est complètement libre.

10. 2021 : les premières puces gratuites !

Quoi de mieux qu’une puce libre ? Une puce gratuite, évidemment ! C’est ce que propose Google avec un récent projet, déjà évoqué plusieurs fois, en association avec d’autres sociétés spécialisées. Mais pourquoi Google se mêlerait-il d’ASIC ?

Le mastodonte de la recherche et de la publicité en ligne s’est investi sans retenue dans « l’Intelligence Artificielle », embauchant les plus grands spécialistes avant que ce soit la mode, au point qu’aujourd’hui la société dépend intimement de cette technologie qui consomme des quantités de calculs ahurissantes. Le département d’IA de Google a réalisé des puces accélératrices, appelées TPU [71] pour ses propres besoins, mais paradoxalement, la société et même sa holding Alphabet n’ont pas de département de conception microélectronique. Les TPU ont donc été réalisées en mode « startup » en interne, dans une branche de la société qui n’était pas prévue pour cela [72]. Google ne compte pas investir dans la création d’un département spécialisé, mais veut faire profiter tous ses départements des avantages des ASIC, à moindre coût et avec un risque minimal.

Comme dans le passé avec Linux et Chrome, la solution de Google est l’Open Source, bien que cet article en expose les limitations (figure 10). Or, qui mieux que Google pourrait ouvrir la brèche et résoudre la question des NDA ? Pour y arriver, la société a missionné Tim Ansell, déjà connu pour ses projets ouverts, pour réunir des partenaires. À l’été 2020, il a annoncé une sorte de ligue extraordinaire :

- FOSSi se charge de l’aspect communautaire et rassemble les contributeurs du monde Open Source.

- Skywater est une fonderie peu connue qui vient de publier l’ensemble de son PDK pour sa technologie 130 nm (figure 11). Cette dernière date de 20 ans, donc elle n’est pas la plus performante, mais son rapport performance/prix est excellent, idéal pour les prototypes.

- Google finance directement la société eFabless [73] pour que cette dernière fournisse gratuitement des prototypes de projets Open Source à leurs concepteurs. 40 projets différents seront sélectionnés par lot de MPW, plusieurs fois par an.

- L’outil Magic sert à vérifier les projets soumis et concevoir le circuit d’accueil, présenté sur la figure 12.

Évidemment, lorsque le service est gratuit, c’est que vous êtes le produit : Google n’accepte pas les projets sous AGPL, EUPL ou certaines variations de Creative Commons, mais « recommande vivement » la licence Apache 2 [74]. En encourageant les expérimentations et les erreurs, l’objectif annoncé est de maximiser les retours d’expérience. Google désire clairement créer un écosystème dans lequel il pourra piocher les outils et les ressources dont il aura besoin dans le futur, pour un coût estimé à quelques millions de dollars, ce qui est dérisoire comparé à la création d’un département dédié.

Conclusion

Alors que l’année 2020 a été catastrophique sur d'innombrables points dans le monde entier, elle fut aussi favorable aux initiatives de circuits intégrés libres, qui sont enfin prises au sérieux après tant d'années d'efforts. Ce basculement de la dynamique industrielle méritait bien une petite remise en perspective !

De nombreux projets libres se sont construits grâce à Internet et 20 ans après le projet F-CPU, le projet Libre-SoC reprend le flambeau, montrant qu'il est enfin possible de réaliser une puce totalement libre et utile. Encore une fois, ce sont des équipes de passionnés qui font tout le travail. Il est même possible de les rémunérer et de faire fructifier leur expérience, sans passer par une corporation ou des contrats handicapants.

Aujourd’hui, créer un circuit intégré est à la portée de bien plus de personnes et Google voudrait rendre cette technologie accessible à quiconque aurait une idée à tester. Évidemment, les bricoleurs auront toujours au moins 20 ans de retard sur les toutes dernières technologies, donc ils ne pourront pas concurrencer Intel ou AMD, mais ce n’est pas l’enjeu réel.

Il est préférable de disposer d’un processeur libre et totalement transparent, même lent, qu’un processeur plus rapide, mais inexploitable ou qui entrave nos droits et nos libertés. Cet enjeu est devenu encore plus critique pour chaque citoyen ces dernières années, alors que les pays sont déstabilisés par la propagation à l’échelle industrielle des « fake news » sur nos propres ordinateurs.

À la fin de 2020, bien qu’il reste encore beaucoup d’efforts à fournir, nous sommes heureusement plus près que jamais d’obtenir une plateforme matérielle libre, capable de faire tourner des logiciels respectueux de notre libre arbitre.

Remerciements

Merci à Ken et John pour l’image, ainsi que Stéphane, Valérie, Olivier, Laura et Raphaël pour les relectures et les suggestions !

Notes

1 Au fait, ai-je suffisamment insisté sur l’importance et les fabuleuses qualités de GHDL ? De nombreux articles sont parus dans GNU/Linux Magazine, il y a une décennie. Les nouvelles fonctionnalités méritent de revenir dessus.

2 Mais oui, mais oui ! Vous avez bien lu ! Il s’agissait en effet d’un projet de voiture électrique Open Source...

3 Un peu plus tard, RISC-V a publié la première spécification d’une extension vectorielle et des réalisations sont apparues, suggérant que l’extension était discutée en privé depuis longtemps, ce qui aurait fourni un avantage commercial aux seuls participants.

Références

[1] Yann Guidon : « Développer en VHDL sous Linux » GLMF no36, 2001 :

http://f-cpu.seul.org/new/lm02.tgz (état de l’art en 2001 de la programmation avec Vanilla VHDL et Simili).

[2] Histoire et description des différentes familles de circuits à fonction logique configurables :

https://fr.wikipedia.org/wiki/Circuit_logique_programmable, https://en.wikipedia.org/wiki/Programmable_logic_device (plus précis).

[3] « 1967 : Application Specific Integrated Circuits employ Computer-Aided Design » :

https://www.computerhistory.org/siliconengine/application-specific-integrated-circuits-employ-computer-aided-design/.

[4] Ken Shirriff examine une puce 8086 contrefaite et découvre un Gate Array à la place : http://www.righto.com/2020/08/inside-counterfeit-8086-processor.html.

[5] Bibliothèque des schémas électroniques des ordinateurs personnels 8 bits Thomson : http://dcmoto.free.fr/documentation/schemas.html.

[6] L’indispensable « Manuel technique du MO5 » par Michel Oury, ed. TOTEK/CEDIC, 1985,scan disponible à :

http://dcmoto.free.fr/documentation/manueltechniquemo5/index.html.

[7] Les ASIC structurés sont un intermédiaire entre ASIC et FPGA : https://en.wikipedia.org/wiki/Structured_ASIC_platform.

[8] Annonce du programme Hard Copy de conversion de FPGA vers circuits prédiffusés à haute densité « Altera joins FPGA-to-ASIC drive as gate arrays come back in vogue » par Anthony Cataldo, 7 septembre 2001 : https://www.eetimes.com/altera-joins-fpga-to-asic-drive-as-gate-arrays-come-back-in-vogue/ « [Lightspeed Semiconductor claims] the volume price is about 80 percent lower than for equivalent Xilinx devices ».

[9] « Transfer from FPGAs for prototype to ASICs for production » Terry Danzer and Cale Entzel, EE Times, novembre 2011 : https://www.eetimes.com/transfer-from-fpgas-for-prototype-to-asics-for-production/ « [...] a migration from an FPGA to an ASIC can cut the production unit cost by up to 50%. » Décrit les contraintes, avantages et inconvénients de traduire un projet FPGA vers un circuit prédiffusé.

[10] https://en.wikipedia.org/wiki/Electron-beam_lithography ou

https://fr.wikipedia.org/wiki/Lithographie_à_faisceau_d'électrons.

[11] Les cellules standard des ASIC : https://en.wikipedia.org/wiki/Standard_cell (l'article n'existe pas en français).

[12] L’annonce de l’initiative Google/Skywater :

https://www.eenewsanalog.com/news/free-chips-courtesy-google-skywater-efabless,

https://hardware.developpez.com/actu/306990/Google-propose-en-open-source-PDK-SkyWater-un-kit-de-conception-de-processus-pour-concevoir-gratuitement-des-puces-en-130-nm/.

[13] Europractice est l'organisme européen de coordination des circuits multiprojets :

https://europractice-ic.com/.

[14] L'organisateur américain du partage des circuits intégrés Metal Oxide Semiconductor Implementation Service : https://mosis.com/https://en.wikipedia.org/wiki/MOSIS.

[15] Le site du CMP à Grenoble propose un agenda pour les prochains lots de circuits, allant de 28 nm à 350 nm de finesse : https://mycmp.fr/technologies/runs-schedule-69.html?annee=2020.

[16] Blog de Sam Zeloof décrivant ses efforts pour réaliser des circuits intégrés dans son garage :

http://sam.zeloof.xyz/category/semiconductor/http://sam.zeloof.xyz/first-ic/.

[17] La page personnelle de Lynn Conway réunissant ses travaux :

http://ai.eecs.umich.edu/people/conway/conway.html.

[18] Archive de documents et ressources éducatives sur l'enseignement de la conception des circuits intégrés durant les années 70-80 : http://ai.eecs.umich.edu/people/conway/VLSI/VLSIarchive.html.

[19] Le « Lions’ book », ou plus précisément « Lions' Commentary on UNIX 6th Edition, with Source Code », est un livre de 1976 contenant le code source commenté et expliqué de la 6e édition de l’UNIX de Bell Labs. Il fut à l’origine conçu comme support de cours pour enseigner la structure des systèmes d'exploitation, puis largement reproduit sous le manteau. Cela a rendu UNIX très accessible et attractif, contribuant à la dominance d'UNIX dans les années 80 et 90 :

https://en.wikipedia.org/wiki/Lions’_Commentary_on_UNIX_6th_Edition,_with_Source_Code.

[20] La « Révolution Mead-Conway » a inspiré l'émergence de l'industrie du semi-conducteur telle que nous la connaissons aujourd'hui, où les bureaux d'étude ne sont plus totalement dépendants des fondeurs : https://en.wikipedia.org/wiki/Mead_&_Conway_revolution.

[21] Liste d'usines de lithographie de circuits intégrés (plus de 1000 actuellement actives) :

https://en.wikipedia.org/wiki/List_of_semiconductor_fabrication_plants.

[22] https://en.wikipedia.org/wiki/Magic_(software), http://www.opencircuitdesign.com/magic/.

[23] L'histoire du projet F-CPU est conservée au chapitre 3 du manuel, disponible à :

http://f-cpu.seul.org/cedric/unstable/F-CPU_manual-0.2.7c-en-color.pdf.

[24] Première annonce du projet F-CPU :

https://news.slashdot.org/story/98/09/08/1646240/the-f-cpu-project-the-freedom-cpu-project.

[25] Calendrier des conférences du 16C3 à Berlin : https://events.ccc.de/congress/1999/fahrplan.html#44.

[26] Tour d'horizon et tutoriel des différents outils VHDL disponibles en 2000-2002 :

http://f-cpu.seul.org/new/VHDL-HOWTO.f-cpu.

[27] La suite logicielle Alliance, créée au début des années 90, est maintenant remplacée par Coriolis : http://coriolis.lip6.fr/

[28] Le site de GHDL, le simulateur VHDL puissant, soucieux des standards et surtout totalement libre : http://ghdl.free.fr/

[29] Yann Guidon, « Rencontre avec Tristan Gingold, l’auteur de GHDL », GLMF no127, mai 2010, pp60-63 : https://connect.ed-diamond.com/GNU-Linux-Magazine/GLMF-127/Rencontre-avec-Tristan-Gingold-l-auteur-de-GHDL.

[30] Il reste quelques traces du site OpenCollector sur la Wayback Machine : https://web.archive.org/web/20140209071318/http://www.opencollector.org/.

[31] Archive du Utopia Computing Webring : https://web.archive.org/web/20040803113251/http://opencollector.org/cgi-bin/utopia/index.

[32] Page d'accueil du « Homebrew CPU webring » : https://www.homebrewcpuring.org/. C'est une des premières listes de projets d'ordinateurs exotiques et originaux, conçus par des amateurs. Pour y être admis, les règles sont de ne pas utiliser d'architecture ou de microprocesseurs existant déjà, de réussir à faire fonctionner (au moins en partie) le système, et d'explorer des technologies parfois surprenantes : NMOS, TTL, DTL, relais électromagnétiques, FPGA ou même EEPROM ! Ce webring fait la part belle aux BMOW (Big Mess of Wires) sur breadboards et a inspiré de nombreux bricoleurs à jouer avec les technologies d'antan. 20 ans après sa création, on peut en partie attribuer à ce site (ainsi qu'à eBay) la mode des processeurs néo-vintage à base de composants discrets et/ou anciens, qui a indirectement motivé de nombreux projets tels que le Gigatron ou le Megaprocessor. Aujourd'hui, l'activité de créer son propre processeur avec des circuits discrets est passée du rang d’obscur hobby de nerds à celui d'art, mêlant histoire et technologie.

[33] Liste des licences acceptées sur le Open Hardware Repository du CERN : https://ohwr.org/licences.

[34] Aperçu de la multiplication des initiatives de matériel open source :

https://en.wikipedia.org/wiki/Open-source_hardware.

[35] Richard Stallman, « Matériel libre et plans libres pour le matériel », mars 2015.Première partie : « Pourquoi nous avons besoin de designs libres » :

https://www.wired.com/2015/03/need-free-digital-hardware-designs/

Deuxième partie : « Voilà comment concevoir du matériel libre » :

https://www.wired.com/2015/03/richard-stallman-how-to-make-hardware-designs-free/

Version française combinée : https://www.gnu.org/philosophy/free-hardware-designs.fr.html.

[36] https://en.wikipedia.org/wiki/OpenCores

[37] le processeur OpenRISC 1000 : https://opencores.org/projects/or1k,

https://openrisc.io/,

https://en.wikipedia.org/wiki/OpenRISC,

https://en.wikipedia.org/wiki/OpenRISC_1200.

[38] https://chips4makers.io/blog/the-buzzword-article-part-2-crowdfunding.html.

[39] Open Hardware Repository est un hébergement gratuit de projets Open Hardware compatibles avec les licences et projets du CERN : https://ohwr.org/.

[40] Le processeur LEON, compatible SPARC V-8 : https://fr.wikipedia.org/wiki/LEON,

https://en.wikipedia.org/wiki/LEON,

https://www.gaisler.com/.

[41] The CPU Shack Museum « ESA Solar Orbiter: When SPARCs Fly » 9 février 2020 :

http://www.cpushack.com/2020/02/09/esa-solar-orbiter-when-sparcs-fly/.

[42] Denis Bodor découvre que le NetGear ReadyNAS Duo embarque un cœur LEON dans Open Silicium no1 de janvier 2011, « Exploration du NetGear ReadyNAS Duo » : https://connect.ed-diamond.com/Open-Silicium/OS-001/Exploration-du-NetGear-ReadyNAS-Duo.

[43] L’adresse opensparc.net redirige aujourd'hui vers

https://www.oracle.com/servers/technologies/opensparc-overview.html.

[44] https://en.wikipedia.org/wiki/OpenSPARC

[45] https://en.wikipedia.org/wiki/OpenPOWER_Foundation

[46] https://openpowerfoundation.org/

[47] https://en.wikipedia.org/wiki/Cell_(microprocessor)

[48] https://openpowerfoundation.org/cores-and-more/

[49] https://en.wikipedia.org/wiki/IBM_A2

[50] https://github.com/openpower-cores/a2ihttps://github.com/openpower-cores/a2o

[51] https://en.wikipedia.org/wiki/IBM_Blue_Gene

[52] Pages décrivant les processeurs RISC-V intégrés dans les FPGA de Microsemi :

https://www.microsemi.com/product-directory/mi-v-embedded-ecosystem/4406-risc-v-cpus, https://www.microsemi.com/product-directory/fpga-soc/5210-mi-v-embedded-ecosystem.

[53] https://en.wikipedia.org/wiki/LatticeMico32

[54] Michael Larabel, « ARM Launches "Facts" Campaign Against RISC-V » 9 juillet 2018 :

https://www.phoronix.com/scan.php?page=news_item&px=ARM-RISC-V-Facts.

[55] https://www.arm.com/resources/designstart

[56] La fondation NLnet : https://en.wikipedia.org/wiki/NLnet, https://nlnet.nl/.

[57] Formulaire pour déposer une demande de financement pour des projets libres :

https://nlnet.nl/propose/.

[58] La page principale du projet Libre-SOC : https://libre-soc.org/.

[59] La page de financement participatif initiale : https://www.crowdsupply.com/libre-risc-v/m-class.

[60] Annonce du projet Libre-RISCV sur Phoronix : https://www.phoronix.com/scan.php?page=news_item&px=Libre-GPU-RISC-V-Vulkan, https://www.phoronix.com/scan.php?page=news_item&px=Libre-RISC-V-Performance-Target.

[61] Le projet EOMA68 : http://rhombus-tech.net/, https://www.crowdsupply.com/eoma68/micro-desktop.

[62] Commentaires sur les buts du projet Libre-SOC :

https://www.phoronix.com/forums/forum/hardware/graphics-cards/1207878-libre-soc-still-persevering-to-be-a-hybrid-cpu-gpu-that-s-100-open-source/page2.

[63] Détails de la logique d’exécution dans le désordre inspirée par le CDC6600 :

https://libre-soc.org/3d_gpu/architecture/6600scoreboard/.

[64] Inscrivez-vous à la mailing list du projet ! http://lists.libre-riscv.org/mailman/listinfo/libre-riscv-dev.

[65] Requête d’aide financière pour la collaboration entre les projets Libre-SOC, nMigen et Coriolis :

https://libre-soc.org/nlnet_2019_coriolis2/.

[66] Le bugtracker du projet Libre-SOC : https://bugs.libre-soc.org/buglist.cgi?component=Milestones&list_id=508&resolution=---.

[67] Chips4Makers est une initiative d’assistance au prototypage de circuits intégrés libres :

https://chips4makers.io/.

[68] Table comparant les caractéristiques des architectures envisagées :

https://libre-soc.org/3d_gpu/arch_comparison/.

[69] Annonce de la décision et explication des raisons du choix d’utiliser l’ISA de POWER :

http://lists.libre-riscv.org/pipermail/libre-riscv-dev/2019-October/003035.html.

[70] Premiers programmes POWER exécutés par Libre-SOC le 3 septembre 2020 sur un FPGA : https://www.youtube.com/watch?v=72QmWro9BSE.

[71] Shan Tang : « A list of Chip/IP for Deep Learning » (2017) :

https://medium.com/@shan.tang.g/a-list-of-chip-ip-for-deep-learning-48d05f1759ae.

[72] Présentation de Timothy Ansell, « Open Source manufacturable PDK for SkyWater 130nm process node », 30 juin 2020 : https://www.youtube.com/watch?v=EczW2IWdnOM

Slides : https://j.mp/du20-sky130.

[73] La société eFabless se charge du Multi-Project Wafer financé par Google :

https://efabless.com/open_shuttle_program.

[74] Google accepte seulement certaines licences dans son offre de prototypage gratuit :

https://efabless.com/open_mpw_faq.

Ajouter à une liste de lecture

Ajouter à une liste de lecture