1. Présentation du cycle de simulation

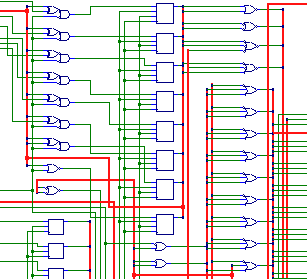

Après avoir écrit le code VHDL de notre circuit, deux voies majeures sont possibles. D'abord, la simulation permet de reproduire le fonctionnement du circuit dans un environnement informatique, ce qui facilite le développement, le rendant plus simple et plus rapide. Ensuite, la synthèse transforme le code de haut niveau en un réseau de portes logiques, qui peuvent ensuite être implantées dans un FPGA ou un ASIC. Dans cet article, nous nous concentrerons uniquement sur la…

- Accédez à tous les contenus de Connect en illimité

- Découvrez des listes de lecture et des contenus Premium

- Consultez les nouveaux articles en avant-première

Ajouter à une liste de lecture

Ajouter à une liste de lecture